#### **Asian Journal of Research in Computer Science**

Volume 16, Issue 4, Page 396-417, 2023; Article no.AJRCOS.110651 *ISSN: 2581-8260*

# Comparing Unbalanced and Balanced CNTFET Ternary Adders and Multipliers with the Corresponding Binary Ones

#### Daniel Etiemble a\* and Ramzi Jaber b

<sup>a</sup>LISN, University Paris Saclay, Gif sur Yvette, France. <sup>b</sup>Electrical and Electronic Engineering Department, Lebanese University, Lebanon.

#### Authors' contributions

This work was carried out in collaboration between both authors. Both authors read and approved the final manuscript.

#### **Article Information**

DOI: 10.9734/AJRCOS/2023/v16i4400

#### **Open Peer Review History:**

This journal follows the Advanced Open Peer Review policy. Identity of the Reviewers, Editor(s) and additional Reviewers, peer review comments, different versions of the manuscript, comments of the editors, etc are available here: https://www.sdiarticle5.com/review-history/110651

Received: 10/10/2023 Accepted: 15/12/2023 Published: 19/12/2023

#### Original Research Article

#### **ABSTRACT**

This paper compares the performance of the ternary adders and multipliers using balanced and unbalanced set of values. We use the 1-trit adders to evaluate the two versions of a 4-trit propagate adder, which are compared with a 6-bit corresponding propagate adder. Similarly, we compare the two types of 2\*2 trit multipliers with a 3\*3 bit multiplier. The simulations with a 32-nm Carbon Nanotuble Field-Effect Transistor (CNTFET) technology show that the binary adders and multipliers are more efficient than the ternary ones that compute the same amount of information.

Keywords: Binary numbers; Ternary Adders; CNTFET; multipliers using balanced.

\*Corresponding author: E-mail: de@lri.fr;

Asian J. Res. Com. Sci., vol. 16, no. 4, pp. 396-417, 2023

#### 1 INTRODUCTION

Ternary circuits can use two different sets of values:

- Unbalanced circuits use 0, 1 and 2 ternary values corresponding to 0,  $V_{dd}/2$  and  $V_{dd}$  levels.

- Balanced circuits use -1, 0 and 1 ternary values corresponding to  $-V_{dd}/2$ , 0 and  $V_{dd}/2$  levels. They are generally quoted as N (Negative), Z (Zero) and P (Positive) to present the ternary numbers.

Most of the proposed ternary full adders use the unbalanced representation. Table 1. presents a comparison of ternary unbalanced full adders presented in the last decade [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11]. Some balanced ternary adders and multipliers have been presented. [12, 13, 14]. Unbalanced ternary multipliers have been presented [15, 16, 17, 18, 19].

The paper is organized as follows:

We present the methodology: (1) CNTFET technology, evaluation of propagation delays, power and power-delay product, chip area. (2)

- Mux-based approch that is used to implement ternary circuits is presented. (3) Binary adders used for comparison are also presented.

- Balanced and unbalanced ternary adders are presented: balanced ones have ternary carry values, while unbalanced ones that are used to implement carry-propagate adders (CPAs) have binary carry values. Their performance are presented and compared. 4-bit CPAs are compared with the two types of 3-trit CPAs.

- Balanced and unbalanced 1-trit multipliers are presented. The balanced one does not generate a carry, while the unbalanced one generates a carry. Their performance are presented and compared. Then a 3\*3 bit multiplier is compared with the two types of 2\*2 trit multipliers. Without simulation, the performance of larger multipliers are also evaluated.

- The conclusion summarizes the results and explains why the binary adders and multipliers are more efficient than the ternary ones that compute the same amount of information.

|                   | CNTFETs | Power     | Max.       | Max. PDP        | Max. EDP                  | Technique                               |

|-------------------|---------|-----------|------------|-----------------|---------------------------|-----------------------------------------|

| TFA / Year        | Count   | $(\mu W)$ | Delay (ps) | $(x10^{-18} J)$ | $(x10^{-27} \text{ J.s})$ | ·                                       |

| In [1] 2011       | 412     | 1.36      | 88         | 12              | 10.5                      | Decoder-Binary-Encoder                  |

| In [2] 2017       | 105     | 1.13      | 68         | 77              | 5.2                       | 2 custom algorithms+TMuxes              |

| In [3] 2017       | 74      | 0.82      | 146        | 120             | 17.5                      | TMUXes                                  |

| In [4] 2018       | 98      | 0.16      | 192        | 31              | 5.9                       | TBDD algorithm                          |

| In [5] 2018       | 89      | 0.44      | 48         | 21              | 1                         | MUXes                                   |

| In [6] 2019       | 142     | 4.62      | 94         | 434             | 40.8                      | Unary ops+MUXes+Encoder                 |

| In [7] 2020       | 106     | 0.13      | 269        | 35              | 9.4                       | Modified Quine-MCluskey algorithm       |

| In [8] 2020       | 49      | 1.23      | 192        | 236             | 45.3                      | Majority-not based Full Adder           |

| In [8] 2020       | 37      | 0.81      | 262        | 212             | 55.5                      | Majority-not based Full Adder           |

| In [9] 2021       | 54      | 0.43      | 47         | 20              | 0.9                       | Unary ops + Decoders+Transmission gates |

| In [10] 2023 TFA1 | 59      | 0.46      | 27         | 12.5            | 0.3                       | Unary ops+MUXEs                         |

| In [10] 2023TFA2  | 55      | 0.22      | 34         | 7.5             | 0.25                      | Unary ops + Muxes                       |

| In [11] 2023      | 48/50   |           |            |                 |                           | Unary ops+MUXES                         |

| In [11] 2023      | 118/128 |           |            |                 |                           | Decoder-Binary-Encoder                  |

**Table 1. TFAs Comparison**

#### 2 METHODOLOGY

#### 2.1 CNTFET Technology

We use CNTFET technology as it is used in most papers presenting ternary or quaternary implementations of adders, multipliers, counters [20], etc. One advantage of CNTFET technology is that the threshold levels of gates only depend on the diameter of individual transistors, which facilitates the design of m-valued circuits. All simulations are done with the 32nm CNTFET parameters of Stanford library [21] that are used by most m-valued CNTFET designers.

#### 2.2 Propagation Delays

For all combinational circuits, the important information is the propagation delay corresponding to the critical paths. We will only present the propagation delays corresponding to these critical paths.

#### 2.3 Power Dissipation and Power-Delay Product (PDP)

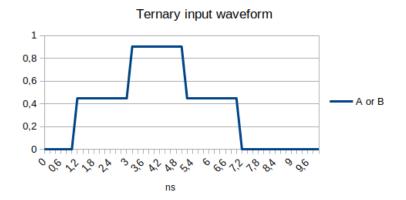

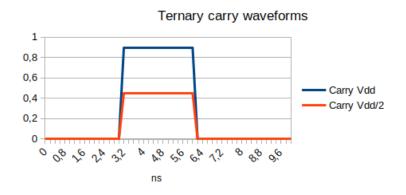

Both power dissipation and PDP directly depends on the duration of the input signals. It is important to use the same input signal for all designs. For all simulations, we use the input waveforms shown in Fig. 1 and Fig. 2 for ternary circuits. We have verified that the delays for 0-2 or 2-0 ternary transitions are always less than ternary transitions 0-1, 1-2, 2-1 or 1-0. The binary waveforms used for the binary adders are presented in Fig. 3.

#### 2.4 Chip Area

We use a rough evaluation of the chip area by summing the diameters of all the used transistors by each circuit. This rough evaluation is a little bit better than the transistor count. In this paper, we use the diameter values presented in Table 2.

Fig. 1. Input waveforms for ternary circuits

Fig. 2. Carry input waveforms for ternary circuits

#### 1 0,8 0,6 Vdd supply 0.4 Vdd/2 supply 0.2 r ტ

#### ns

Binary Input and carry waveforms

Fig. 3. Input waveforms for binary circuits

**Table 2. Transistor diameters**

|    | n  | Diameter(nm) |

|----|----|--------------|

| D1 | 10 | 0.783        |

| D2 | 19 | 1.487        |

| D3 | 29 | 2.270        |

| D4 | 37 | 2.896        |

Table 3. Basic operations for implementing ternary circuits

| Α | $A_n$ | $A_p$ | A1 | A2 | A001 | A011 | Etc |

|---|-------|-------|----|----|------|------|-----|

| 0 | 2     | 2     | 1  | 2  | 0    | 0    |     |

| 1 | 0     | 2     | 2  | 0  | 0    | 1    |     |

| 2 | 0     | 0     | 0  | 1  | 1    | 1    |     |

#### The Mux-based Implementation 2.5

Implementation of ternary circuits can used different techniques: Paper [11] presents a detailed examination of the two opposite techniques, which are "Decoders-Binary-Encoders" and "MUX-based" implementations. The most efficient one is the MUX-based one, as shown by a detailed examination of Table 1.

The MUX approach uses the operations that are shown in Table 3. Ternary multiplexers are used to switch the correct values to the outputs.

Similar circuits are used by unbalanced and balanced circuits.

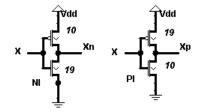

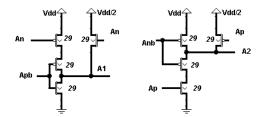

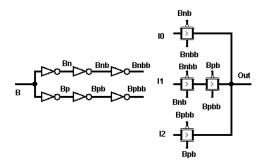

$A_n$  and  $A_p$  unary functions are implemented by the threshold detectors shown in Fig. 4. The  $A^1$  and  $A^2$  operators (Fig. 5) are derived from  $A_n$  and  $A_p$ outputs of the threshold detectors. The 3-input MUX circuit is shown in Fig. 6. Inverters delivering Bn and Bp are the threshold detectors presented in Fig. 4. Inverters delivering Bnb, Bnp, Bnpbb and Bpbb are usual binary inverters. Bnbb and Bpbb have higher driving capabilities than Bn and Bp.

#### 2.6 **Comparison with Binary Circuits**

Any proposal of ternary circuits should be compared with the binary circuits computing the same amount of information, either to prove or disprove their interest:

- · Ternary adders should be compared with binary adders.

- · Ternary multipliers use 1-trit multipliers and ternary adders. 1-bit multiplier is implemented with a AND gate.

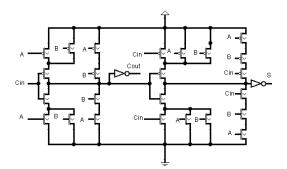

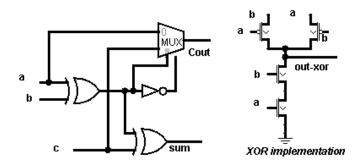

We use two types of full adders

- The first one is the typical 28T full adder (Fig. 7).

- · The second one is the 14T full adder presented in Fig. 8.

- · A detailed analysis of the performance of these binary adders can be found in [11].

Fig. 4. Threshold detectors

Fig. 5.  ${\cal A}^1$  and  ${\cal A}^2$  circuits

Fig. 6. 3-input MUX with ternary control

Fig. 7. 28T binary full adder

Fig. 8. 14T binary full adder

#### 3 1-TRIT ADDERS

#### 3.1 Unbalanced 1-trit Adders (UTFA)

There are two types of unbalanced 1-trit adders:

- The 1-trit adder for building n-trit adders. a and b inputs and S output are ternary. Input and output carries

are binary.

- · The ternary counter also called compressor for which all values (inputs, output and carries) are ternary.

Table 4 presents the combined truth table. The whole table corresponds to the ternary counter. Only the columns  $C_{in}$ =0 and  $C_{in}$ =1 should be considered for the 1-trit adder.

The Mux approach is based on a different way to consider Table 4:

Table 4. Truth table of a ternary full adder with ternary carries

|   | ( | $C_{in}$ =0 | )          |   | ( | $C_{in}=1$ |            |   | ( | $C_{in}$ =2 | 2          |

|---|---|-------------|------------|---|---|------------|------------|---|---|-------------|------------|

| а | b | $S_0$       | $C_{out0}$ | а | b | $S_1$      | $C_{out1}$ | а | b | $S_2$       | $C_{out2}$ |

| 0 | 0 | 0           | 0          | 0 | 0 | 1          | 0          | 0 | 0 | 2           | 0          |

| 0 | 1 | 1           | 0          | 0 | 1 | 2          | 0          | 0 | 1 | 0           | 1          |

| 0 | 2 | 2           | 0          | 0 | 2 | 0          | 1          | 0 | 2 | 1           | 1          |

| 1 | 0 | 1           | 0          | 1 | 0 | 2          | 0          | 1 | 0 | 0           | 1          |

| 1 | 1 | 2           | 0          | 1 | 1 | 0          | 1          | 1 | 1 | 1           | 1          |

| 1 | 2 | 0           | 1          | 1 | 2 | 1          | 1          | 1 | 2 | 2           | 1          |

| 2 | 0 | 2           | 0          | 2 | 0 | 0          | 1          | 2 | 0 | 1           | 1          |

| 2 | 1 | 0           | 1          | 2 | 1 | 1          | 1          | 2 | 1 | 2           | 1          |

| 2 | 2 | 1           | 1          | 2 | 2 | 2          | 1          | 2 | 2 | 0           | 2          |

When  $C_{in}$ =0

- When B=0 then Sum=A

- When B=1 then Sum = (A+1) mod(3) quoted as  $A^1$

- When B=2 then Sum = (A+2) mod(3) quoted as  $A^2$

- When B=0 then  $C_{out}$ =0

- When B=1 then  $C_{out}$ =1 when A=2 else 0

- When B=2 then  $C_{out}$ =1 when A>0 else 0

When  $C_{in}$ =1

- When B=0 then  $Sum=A^1$

- When B=1 then Sum= $A^2$

- When B=2 then Sum= A

- When B=0 then  $C_{out}$ =1 when A=2 else 0

- When B=1 then  $C_{out}$ =1 when A>0 else 0

- When B=2 then  $C_{out}$ =1

When  $C_{in}$ =2 (Only for the ternary counter)

- When B=0 then Sum= $A^2$

- When B=1 then Sum=A

- When B=2 then  $Sum=A^2$

- When B=0 then  $C_{out}$ =1 when A>0 else 0

- When B=1 then  $C_{out}$ =1

- When B=2 then  $C_{out}$ =2 when A>1 else 1

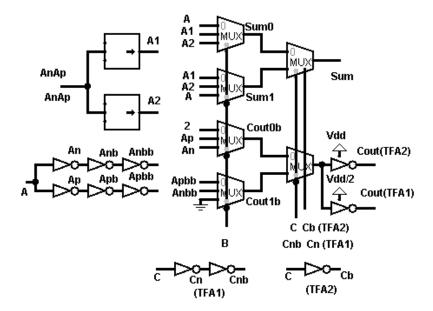

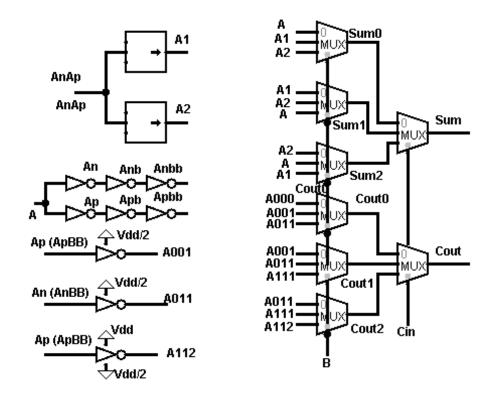

In the two left columns of Table 4, the binary input and output carry values are 0,1 while A and B inputs have 0,1,2 values. However, when implementing ternary adders, the carry levels can be 0 and  $V_{dd}/2$  (corresponding to 0,1 values) or 0 and  $V_{dd}$  (corresponding to 0,2 values). The two different versions named TFA1 and TFA2 are shown in Fig. 9.

$V_{dd}$  carry swing can be used as  $C_{in}$  only controls the final MUXes and  $C_{out}$  can also have a  $V_{dd}$  swing . There are few differences between  $V_{dd}/2$  and  $V_{dd}$  carry versions that are outlined in Fig. 9. The  $V_{dd}/2$  version uses the inverter implementing  $A_n$  to get  $C_n$  and the final carry inverter has a 0.45V power supply. For the  $V_{dd}$  version,  $C_{in}$  and  $C_{out}$  use inverters with  $V_{dd}$  power supply.

Fig. 9. Unbalanced 1-trit Full Adder (Mux approach)

The 1-trit unbalanced adder is shown in Fig. 9. They have a common part:

- Two 3-input MUXes controlled by B switch A,  $A^1$ ,  $A^2$  to  $Sum_0$  and  $Sum_1$ . Two other 3-input MUXes controlled by B switch different binary carry values to  $\overline{C_{out0}}$ . and  $\overline{C_{out1}}$ . It should be noticed that these binary values are 0,2.

- One final MUX controlled by  $C_{in}$  switches either  $Sum_0$  or  $Sum_1$  to Sum while another one switches either  $\overline{C_{out0}}$  or  $\overline{C_{out1}}$  to  $\overline{C_{out}}$ .

For TFA1, the final  $C_{out}$  with 0,1 values is obtained using an inverter with  $V_{dd}/2$  power supply. The final inverter for the carry output is introduced to avoid a long chain of MUX3 in the carry propagation of Carry Propagate Adders (CPA) that would degrade the propagation times. The resulting 1-trit full adder is shown in Fig. 9. The 2-input final MUXes are controlled by a binary value  $(C_{in})$ . They use the typical 2-input

MUXes with binary control. TFA2 uses a final binary inverter with  $V_{dd}$  power supply. The control of the MUX2s are different for TFA1 and TFA2.

The (3,2) unbalanced ternary counter is shown in Fig. 10. It is not useful to implement n-trit adders. We present it as it is similar to the balanced 1-trit adder.

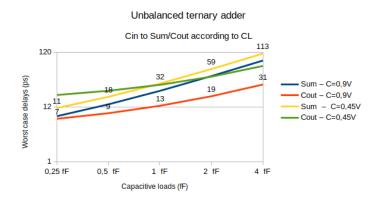

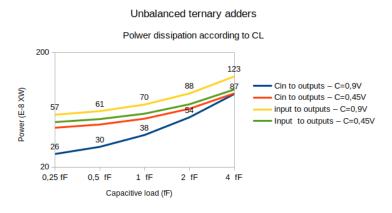

For unbalanced ternary adders, Fig. 11. presents the Input to Sum/ $C_{out}$  delays according to CL for the two versions (0.45 and 0.9V carry swings). The log-log scale shows that the delays roughly increase linearly with CL. Sum delays are similar for the two versions. The  $C_{out}$  delays are less sensitive to CL, and less for 0.45V than for 0.9V carry swing. Fig. 12. presents the  $C_{in}$  to Sum/ $C_{out}$  delays. The  $C_{out}$  delays are slower with 0.9 V swing, which is the reason to introduce it for CPAs. Fig. 13. presents the power dissipation according to CL. It increases more than linearly with CL.

Fig. 10. Unbalanced Ternary (3,2) counter

#### Unbalanced ternary adders Input to Sum/Cout according to CL 200 150 130 120 116 Worst case delay (ps) 91 Sum - C=0,9V Cout - C=0,9V Sum - C=0,45V Cout - C=0,45V 0,25 fF 0,5 fF 2 fF 1 fF 4 fF Capacitive loads (fF)

Fig. 11. Input to Sum/ $C_{out}$  of unbalanced ternary adders according to CL

Fig. 12.  $C_{in}$  to Sum/ $C_{out}$  of unbalanced ternary adders according to CL

Fig. 13. Power dissipation of unbalanced ternary adders according to CL

#### 3.2 Balanced 1-trit Adders (BTFA)

Table 5. presents the truth table of a balanced ternary adder. Table 6. presents the same table by replacing N by 0, Z by 1 and P by 2 to establish the correspondence between 0,  $V_{dd}/2$  and  $V_{dd}$  and 0,1,2. This allow a direct comparison between the unbalanced and balanced implementations.

$C_{in}$ =N  $C_{in}$ =Z  $C_{in}$ =P sP b sN CtN b sΖ CZ b CP а а а Z Ν Р Ν Ν Z Ν Ν Ν Ν Ν Ν Ρ Ζ Ζ Ζ Ν Ζ Ζ Ζ Ν Ν Ν Ν Ν Ρ Ν Ζ Ν Ρ Ζ Ζ Ν Ρ Ρ Ζ Ζ Ν Ρ Ν Ζ Ν Ν Ζ Ζ Ν Ζ Ζ Ζ Ζ Ζ Ζ Ζ Ζ Ζ Ζ Ζ Ζ Ν Ζ Ρ Ζ Ζ Ζ Ρ Ρ Ζ Ζ Ρ Ν Ρ Ρ Ν Ν Ζ Ρ Ν Ζ Ζ Ρ Ν Ρ Ζ Ρ Ζ Ζ Ζ Ρ Ζ Ρ Ζ Ρ Ζ Ν Ρ Р Ρ Ρ Р Р Р Ρ Ζ Ν Ρ Ρ Ζ

Table 5. Truth table of a balanced ternary adder

Table 6. Truth table of a balanced ternary adder (N=0; Z=1; P=2)

|   | C | $_{in}$ =0 |       |   | C | $_{in}$ =1 |       |   | C | $_{in}$ =2 |       |

|---|---|------------|-------|---|---|------------|-------|---|---|------------|-------|

| b | а | $S_0$      | $C_0$ | а | b | $S_1$      | $C_1$ | а | b | $S_2$      | $C_2$ |

| 0 | 0 | 1          | 0     | 0 | 0 | 2          | 0     | 0 | 0 | 0          | 1     |

| 0 | 1 | 2          | 0     | 0 | 1 | 0          | 1     | 0 | 1 | 1          | 1     |

| 0 | 2 | 0          | 1     | 0 | 2 | 1          | 1     | 0 | 2 | 2          | 1     |

| 1 | 0 | 2          | 0     | 1 | 0 | 0          | 1     | 1 | 0 | 1          | 1     |

| 1 | 1 | 0          | 1     | 1 | 1 | 1          | 1     | 1 | 1 | 2          | 1     |

| 1 | 2 | 1          | 1     | 1 | 2 | 2          | 1     | 1 | 2 | 0          | 2     |

| 2 | 0 | 1          | 1     | 2 | 0 | 1          | 1     | 2 | 0 | 2          | 1     |

| 2 | 1 | 1          | 1     | 2 | 1 | 2          | 1     | 2 | 1 | 0          | 2     |

| 2 | 2 | 2          | 1     | 2 | 2 | 0          | 2     | 2 | 2 | 1          | 2     |

The operation of BTFA is described below:

When  $C_{in}$ =0

- When B=0 then Sum=A

- When B=1 then Sum =  $(A+1) \mod(3)$  guoted as  $A^1$

- When B=2 then Sum = (A+2) mod(3) quoted as  $A^2$

- When B=0 then  $C_{out}$ =0

- When B=1 then  $C_{out}$ =1 when A=2 else 0

- When B=2 then  $C_{out}$ =1 when A>0 else 0

When  $C_{in}$ =1

- When B=0 then  $Sum=A^2$

- When B=1 then Sum=A

- When B=2 then  $Sum=A^1$

- When B=0 then  $C_{out}$ =1 when A=2 else 0

- When B=1 then  $C_{out}$ =1 when A>0 else 0

- When B=2 then  $C_{out}$ =1

When  $C_{in}$ =2 (Only for the ternary counter)

- When B=0 then Sum=A

- When B=1 then Sum=A<sup>1</sup>

- When B=2 then  $Sum=A^2$

- When B=0 then  $C_{out}$ =1

- When B=1 then  $C_{out}$ =2 when A>1 else 1

- When B=2 then  $C_{out}$ =2 when A>0 else 1

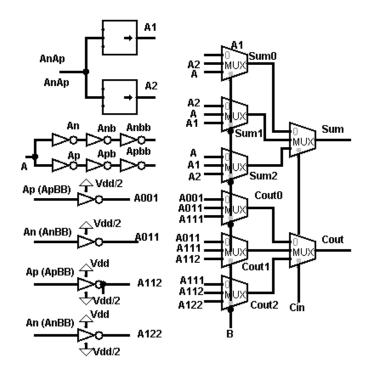

We define two versions of the balanced ternary adder.

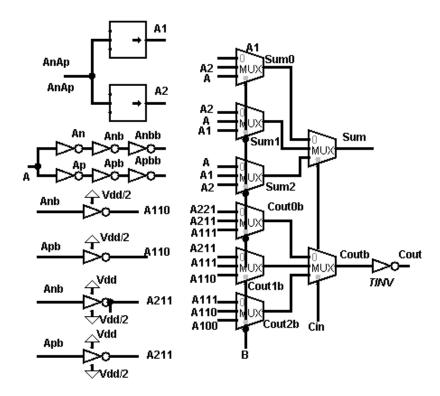

Fig. 14. Balanced ternary adder - Version 1

- The first one is presented in Fig. 14. It corresponds to the truth table.

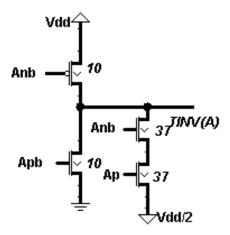

- The second one is presented in Fig. 15. As for the unbalanced version, it uses an inverter to avoid a long chain of MUX3 in CPAs. However, as the balanced carries are ternary, this inverter is a ternary one. The used ternary inverter is shown in Fig. 16. A lot of ternary inverters have been proposed, with 4, 5, 6, 8 transistors. However, most of them have conflicting behaviors of transistors for the intermediate level, which increase power dissipation. Our implementation has a total of 12 transistors (including 4 inverters to generate  $a_n$ ,  $a_{nb}$ ,  $a_p$  and apb) but has less power dissipation than most implementations with less transistors.

Fig. 15. Balanced ternary adder - Version 2

Fig. 16. Ternary inverter

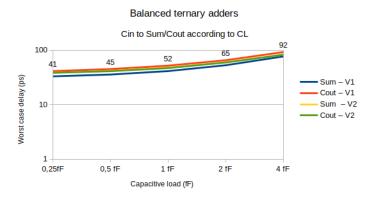

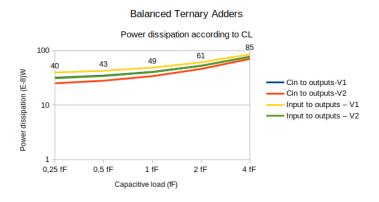

Fig. 17, 18 and 19 respectively present the Input to  $Sum/C_{out}$  delays, Carry to  $Sum/C_{out}$  delays and power dissipation according to CL. There are few differences between V1 and V2 versions.

# Balanced Ternary Adders Input to Sum/Output according to CL 120 55 58 65 74 — Sum-V1 — Cout-V1 — Sum-V2 — Sum-V2 — Sum-V2 — Sum-V2 — Capacitive load (fF)

Fig. 17. Input to Sum/ $C_{out}$  of balanced ternary adders according to CL

Fig. 18.  $C_{in}$  to Sum/ $C_{out}$  of balanced ternary adders according to CL

Fig. 19. Power dissipations of balanced ternary adders according to CL

## 3.3 Comparing the Balanced and Unbalanced 1-trit Adders

Fig. 20. compares these two 1-trit adders:

- $\Sigma Di$  for the balanced version is roughly x3  $\Sigma Di$  of the unbalanced version. It comes from using ternary versus binary carries : 8 MUX3 versus 4 MUX3 and 2 MUX2, more circuits to generate the carry values, etc.

- In Carry-Propagate Adders, the critical path is

C<sub>in</sub> to C<sub>out</sub>. The unbalanced version has smaller

C<sub>in</sub> to C<sub>out</sub> delays (x3 smaller delay when using the 0.9V carry swing).

- Input to Sum/Output are smaller for the balanced version. However, Input to  $C_{out}$  delay is significant only for the first stage of a CPA.

Clearly, the unbalanced version is the best one for implementing CPAs.

#### Performance with CL=2fF 300 246 229 250 200 150 ■ BTFA-V1 150 105<sup>121</sup> 105 ■ BTFA-V2 7872 65<sub>59</sub>43 100 UTFA-C=0.45V 7469 53<sup>5959</sup>44 7273 6151 ■ UTFA-C=0.9V 50 INDUI TO SUM UPS 410in

#### 1-trit balanced and unbalanced adders

Fig. 20. Comparing 1-trit balanced and unbalanced adder (CL=2fF)

Fig. 21. Comparing 4-trit and 6-bit CPAs (CL=2fF)

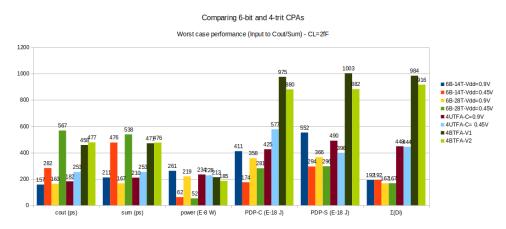

Fig. 21. compares balanced and unbalanced 4-trit CPAs with 6-bit CPAs:

- · The two versions of the balanced 4-trit CPA have similar performance. The two versions of unbalanced CPAs have also similar performance. However, the unbalanced CPAs has delays x2 smaller than the balanced ones.

- There are few differences between the binary CPAs using 14T and 28T. The 28T version has less chip area than 14T version because it only uses transistor with Di=1.487 nm while the 14T version uses transistors with 2,896 nm for XOR gates and MUX2. When 0.45V  $V_{dd}$  is used, power is roughly divided by 4.

- · The delays of the 4-trit unbalanced CPAs are smaller than the corresponding ones of the 6-bit CPAs only for the 0.45V binary  $V_{dd}$ .

- · The power of the same unbalanced CPAs are smaller than the power of the 6-bit CPAs only for the 0.9V binary  $V_{dd}$ .

- The  $\Sigma Di$  of the binary CPAs are more than

x2 smaller than the unbalanced CPAs and x4.5 smaller than the balanced CPAs.

Clearly, the 6-bit CPA are more efficient than the 4-trit CPAs. The balanced 4-trit CPAs are outperformed by the unbalanced ones.

#### 1-TRIT MULTIPLIERS

#### 4.1 **Unbalanced 1-trit Multipliers**

Table 6 presents the truth table of the unbalanced 1-trit multiplier. This multiplier generates both a product term and a carry term. For a mux-based implementation, Table 6. can be rewritten as

- When Bi=0 then Pi=0 and Ci=0

- When Bi=1 then Pi=Bi and Ci=0

- When Bi=2 then Pi= {0,2,1} and Ci={0,0,1} for  $Ai = \{0,1,2\}$

The X021 and X001 unary operators and a ternary multiplexer are needed to implement the 1-trit multiplier.

| Bi | Ai  | Pi | Ci |  |

|----|-----|----|----|--|

| 0  | 0   | 0  | 0  |  |

| 0  | 1   | 0  | 0  |  |

| 0  | 2   | 0  | 0  |  |

| 1  | 0   | 0  | 0  |  |

| 4  | 4 1 | 4  | Λ  |  |

2 2 0 1 2 0 0 0 2 2 0 1 2 2 1

Table 6. Truth Table of a 1-trit unbalanced multiplier

Fig. 22. Unbalanced ternary multiplier performance according to CL

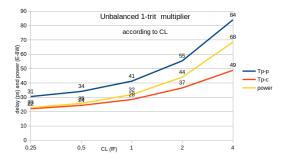

Fig. 22. presents the delay and power of the unbalanced multiplier according to CL.

#### 4.2 Balanced 1-trit Multipliers

Table 7 presents the truth table of a balanced 1-trit multiplier. The left part uses the N(-1), Z(0) and P (+1) notations of the balanced ternary representation. The right part presents the correspondence with the ground level (0), middle level (1) and  $V_{dd}$  (2) of the corresponding circuits. It should be noticed that the 1-trit balanced multiplier does not generate a carry output.

| Bi               | Ai | Prod.                 | Ai | Bi | Prod. |

|------------------|----|-----------------------|----|----|-------|

| N                | N  | Р                     | 0  | 0  | 2     |

| Ν                | Ζ  | Z                     | 0  | 1  | 1     |

| Ν                | Р  | N                     | 0  | 2  | 0     |

| Z                | Ν  | Z                     | 1  | 0  | 1     |

| Z                | Ζ  | Z                     | 1  | 1  | 1     |

| Z<br>Z<br>Z<br>P | Р  | Z<br>N<br>Z<br>Z<br>Z | 1  | 2  | 1     |

| Р                | Ν  | N                     | 2  | 0  | 0     |

| Р                | Ζ  | N<br>Z                | 2  | 1  | 1     |

| Р                | Р  | Р                     | 2  | 2  | 2     |

|                  |    |                       |    |    |       |

Table 7. Truth Table of a 1-trit multiplier

For the mux based implementation, Table 7. can be rewritten as:

- When Bi=0 then Prod={2,1,0} when A={0,1,2}. It is implemented by a ternary inverter.

- When Bi=1 then Prod=1

- When Bi=2 then Prod=Ai

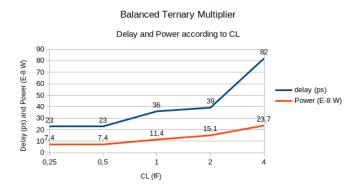

Fig. 23. Balanced ternary multiplier performance according to CL

Fig. 23. presents the delay and power of the unbalanced multiplier according to CL.

#### 4.3 Comparing Balanced and Unbalanced 1-trit Multiplier

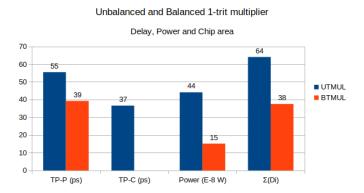

Fig. 24. summarizes the comparison between the two different versions

- There is no significant difference for worst-case propagation delays

- · Power dissipation is roughly 3x lower for the balanced version, due to the absence of carry generation.

- For the same reason,  $\Sigma Di$  is about x2 smaller for the balanced version.

As the balanced version does not generate a carry: there are n lines in the reduction tree of a n\*n trit multiplier, when there are 2n lines in the unbalanced version.

Fig. 24. Unbalanced and Balanced 1-trit multiplier with 2fF capacitive loads

### 4.4 Comparing 2\*2 Trit Balanced and Unbalanced Multipliers with a 3\*3 bit Multiplier

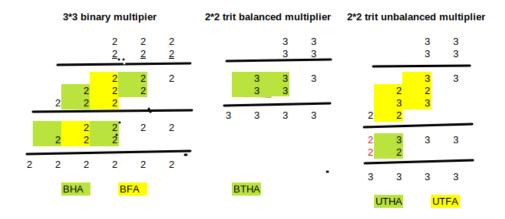

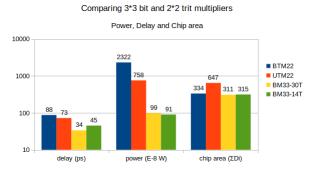

While it makes sense to compare the two versions of 1-trit multiplier, it is not fair to compare them with the 1-bit multiplier, which is only an AND gate. We compare now a 3\*3 bit multiplier, with the two versions of 2\*2 trit multipliers (Fig. 25). In this figure, 3 corresponds to a ternary value and 2 to a binary one. The 3\*3 bit multiplier computes 6 bits of information versus 6.34 bit for the 2\*2 trit multipliers. These multipliers are quite simple. The ternary balanced multipliers only use two balanced ternary half adders.

Fig. 25. 3\*3 bit and 2\*2 trit multipliers

The 3\*3 bit multiplier use 9 and gates (NAND+Inverter), 3 binary half adders and 3 binary full adders. For our simulations, we used 6 binary full adders.

The worst-case delay (WC) of the 3\*3 bit multiplier is obtained by multiplying x11\*111 with  $x=\{0,1,0\}$ . The corresponding outputs are then  $\{010101, 110001, 010101\}$ . m5 outputs are  $\{0,1,0\}$  and m2 outputs are  $\{1,0,1\}$ . For the ternary multipliers, x2\*22 delivers the WC delay with  $x=\{0,1,2,1,0\}$ . The corresponding outputs are then  $\{0121, 1111, 2101, 1111, 0121\}$ . m3 outputs are then  $\{0,1,2,1,0\}$  and m1 outputs are  $\{2,1,0,1,2\}$ . Fig. 26. summarizes the comparison:

- · The two binary multipliers have similar performance.

- The delay of the ternary multipliers are close. However, the unbalanced chip area is close to x2 the balanced one, while the power dissipation of the balanced one is close to x3 the power of the unbalanced one.

- The two ternary multipliers are outperformed by the two binary ones. Delays are x1.5 to x2 greater. Power is x8 to x25 greater. Chip area is equivalent for the balanced version. However, it is x2 for the unbalanced one.

Fig. 26. Comparing 2\*2 trit and 3\*3 bit multipliers

#### 4.5 Comparing Larger Multipliers without Simulations

Simulating larger ternary and binary multipliers would be more significant, but would need huge simulation times. However, without simulation, it is possible to evaluate the chip area of different multipliers computing the same amount of information. It is also possible to evaluate the worst case propagation delay.

|     |       | Number |      |     | ΣDi/unit |    | ΣDi (total |       |      |

|-----|-------|--------|------|-----|----------|----|------------|-------|------|

|     | TB4*4 | TU4*4  | B6*6 |     |          |    | TB4*4      | TU4*4 | B6*6 |

| MUL | 16    | 16     | 36   | 38  | 64       | 14 | 608        | 1024  | 504  |

| HA  | 4     | 7      | 11   | 92  | 78       | 18 | 368        | 546   | 198  |

| FA  | 8     | 17     | 23   | 178 | 104      | 47 | 1424       | 1768  | 1081 |

|     |       |        |      |     |          |    | 2400       | 3338  | 1783 |

|     |       |        |      |     |          |    | 1 2        | 1 0   | 1    |

|     |       | Number |        |     | ΣDi/unit |    | ΣDi (total |       |      |

|-----|-------|--------|--------|-----|----------|----|------------|-------|------|

|     | TB8*8 | TU8*8  | B12*12 |     |          |    | TB4*4      | TU4*4 | B6*6 |

| MUL | 64    | 64     | 144    | 38  | 64       | 14 | 2432       | 4096  | 2016 |

| HA  | 17    | 20     | 31     | 92  | 78       | 18 | 1564       | 1560  | 198  |

| FA  | 47    | 73     | 107    | 178 | 104      | 47 | 8366       | 7592  | 5029 |

|     |       |        |        |     |          |    | 12362      | 13248 | 7243 |

|     |       |        |        |     |          |    | 1.7        | 1.8   | 1    |

Fig. 27.  $\Sigma(Di)$  of 4\*4 trit and 6\*6 bit multipliers and  $\Sigma(Di)$  of 8\*8 trit and 12\*12 bit multipliers

Higher part of Fig. 27. compares 4\*4 trit and 6\*6 bit multipliers. Lower part of this figure compares 8\*8 trit and 12\*12 bit multipliers. The different multipliers use (3,2) adders in the Wallace reduction trees and carry-propagate

adders for the final sum (this is the only difference with actual combinational multipliers that would use fast adders for the final sum). The unbalanced ternary versions use more chip area than the balanced one: this is due to the carries generated by the multipliers that double the number of lines to reduce. In both case, the ternary versions use more than x1.8 chip area than the binary one for the unbalanced version and x1.3 and x1.7 for the balanced version.

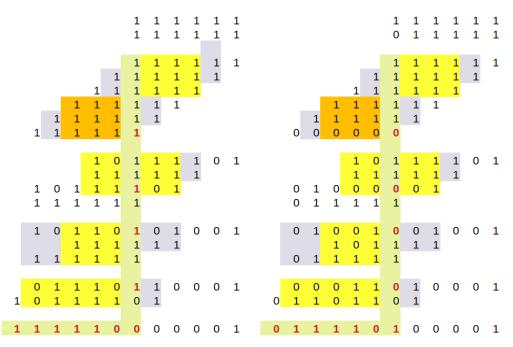

For a 6\*6 bit multiplier, Fig. 28 shows how the worst case propagation delay can be evaluated. There is the propagation delay of the 1-digit multiplier. Then the worst case delay corresponds to the vertical longest path in the reduction tree followed by the horizontal left propagation delay for the remaining bits of the carry propagate adder. These delays have a green color on the two parts of Fig. 28. We use the following notation:

- TpMul is the delay of the 1-digit multiplier.

- TpFAI2Sum is the input to Sum delay of the 1-digit Full Adder.

- TpFAI2Cout is the input to  $C_{out}$  delay of the 1-digit Full Adder.

- $TpFAC_{in}2C_{out}$  is the  $C_{in}$  to  $C_{out}$  delay of the 1-digit Full Adder.

The evaluation of WC delays of binary multipliers have been done with 28T binary full adders.

Fig. 28. Worst case delay through multipliers and Wallace reduction tree

For the 6\*6 bit multiplier, the WC delay is:  $T_pMul + 3T_pFAI2Sum + T_pFAI2C_{out} + 5T_pFAC_{in}2C_{out}$

Higher part of Fig. 29. compares the evaluated WC delays of the two types of 4\*4 ternary multipliers and a 6\*6 bit multiplier. Lower part of the Fig. 29. compares 8\*8 trit multipliers with a 12\*12 bit multiplier. WC delays of the two types of ternary multipliers are close. However, they are x1.7 to 2.1 the propagation delays of the binary multipliers computing the same amount of information. These results are not surprising:

• There are x2.25 more binary multipliers than ternary ones. However, the ternary multipliers are x2.7 and x4.6 slower than the binary ones.

There are less half adders and full adders for the ternary versions, but the ternary half adders and full

adders are slower than the corresponding binary ones.

The evalution of WC delays that has been done is not as precise as simulations. However, it provides a significant information.

The delays and chip area ratio between ternary and binary adders and multipliers should not be considered as absolute values. For the different components, delays and chip area depend on the chosen diameter values of the transistors. However, as the ratios are between x1.7 and x2.3, different design diameter sizes would not change the results of the comparisons.

D = 1 = - - // 1 = - 14

| _                                 |                | Number         |                 |                 | Delay/Unit                  |                             |                  | Delay                          |                        |

|-----------------------------------|----------------|----------------|-----------------|-----------------|-----------------------------|-----------------------------|------------------|--------------------------------|------------------------|

| ĺ                                 | TB44           | TU44           | B66             | TB              | TU                          | Bin                         | TB44             | TU44                           | B66                    |

| Multiplier                        | 1              | 1              | 1               | 36              | 55                          | 15                          | 36               | 55                             | 15                     |

| FAI2Sum                           | 1              | 2              | 3               | 72              | 105                         | 27                          | 72               | 210                            | 81                     |

| FAI2Cout                          | 1              | 1              | 1               | 105             | 19                          | 47                          | 105              | 19                             | 47                     |

| FACin2Cout                        | 4              | 3              | 5               | 59              | 44                          | 21                          | 236              | 132                            | 105                    |

| FACIN2Sum                         |                | 1              |                 |                 | 121                         | 24                          |                  | 121                            | 0                      |

|                                   |                |                |                 |                 |                             |                             | 449              | 416                            | 248                    |

|                                   |                |                |                 |                 |                             |                             | 1,8              | 1,7                            | 1                      |

|                                   |                |                |                 |                 |                             |                             |                  |                                |                        |

|                                   |                |                |                 |                 |                             |                             |                  |                                |                        |

|                                   |                | Number         |                 |                 | Delay/Unit                  |                             |                  | Delay                          |                        |

| i                                 | TB88           | Number<br>TU88 | B1212           | ТВ              | Delay/Unit<br>TU            | Bin                         | TB44             | Delay<br>TU44                  | B66                    |

| Multiplier                        | TB88<br>1      |                | B1212<br>1      | TB<br>36        |                             |                             | TB44<br>36       |                                | B66<br>15              |

| Multiplier<br>FAI2Sum             | TB88<br>1<br>3 |                | B1212<br>1<br>4 |                 | TU                          | Bin                         |                  | TU44                           |                        |

|                                   | 1              | TU88<br>1      | 1               | 36              | TU<br>55                    | Bin<br>15                   | 36               | TU44<br>55                     | 15                     |

| FAI2Sum                           | 1              | TU88<br>1      | 1<br>4          | 36<br>72        | TU<br>55<br>105             | Bin<br>15<br>27             | 36<br>216        | TU44<br>55<br>420              | 15<br>108              |

| FAI2Sum<br>FAI2Cout               | 1<br>3<br>1    | TU88<br>1      | 1<br>4<br>1     | 36<br>72<br>105 | TU<br>55<br>105<br>19       | Bin<br>15<br>27<br>47       | 36<br>216<br>105 | TU44<br>55<br>420<br>19        | 15<br>108<br>47        |

| FAI2Sum<br>FAI2Cout<br>FACin2Cout | 1<br>3<br>1    | TU88<br>1      | 1<br>4<br>1     | 36<br>72<br>105 | TU<br>55<br>105<br>19<br>44 | Bin<br>15<br>27<br>47<br>21 | 36<br>216<br>105 | TU44<br>55<br>420<br>19<br>308 | 15<br>108<br>47<br>231 |

Fig. 29. WC delays of 4\*4 trit and 6\*6 bit multipliers and WCDelay of 8\*8 trit and 12\*12 bit multipliers

#### 5 CONCLUDING REMARKS

Two versions of balanced ternary adders have been compared with two versions of unbalanced ones. The balanced version does not provide advantage as it uses far more chip area. The results are similar when implementing 4-trit CPAs. The two versions are less efficient than the binary ones when comparing 4-trit CPAs and 6-bit CPAs.

1-trit balanced and unbalanced multipliers have been compared. The balanced version has two advantages:

- As it does not generate a carry, it has smaller delays, smaller power dissipation and smaller chip area.

- The balanced version directly operates positive and negative numbers, while the unbalanced one only operate on positive numbers.

However, when comparing 2\*2 trit multipliers, the

balanced version uses x2 less chip area, but has a small disadvantage in delay and x3 more power dissipation.

While 2\*2 trit multipliers and 3\*3 bit multipliers have similar chip areas, the ternary multipliers have larger delays and power dissipation from x7 to x25 the power of the binary ones. It comes from the larger complexity of the 1-trit adders compared to a AND gate and the larger complexity of the 1-trit adders compared to the binary ones.

This study shows that the ternary approach does not improve the performance of the binary approach for typical combinational circuits such as adders and multipliers.

#### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

#### REFERENCES

- [1] Lin S, Kim YB, Lombardi F. CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnology. 2011;10(2):217-225. DOI: 10.1109/TNANO.2009.2036845

- [2] Srinivasu B, Sridharan K. A synthesis methodology for ternary logic circuits in emerging device technologies. IEEE Trans. Circuits Syst. I. 2017;64(8):2146-2159. DOI: 10.1109/TCSI.2017.2686446

- [3] Tabrizchi S, Panahi A, Sharifi F, Navi K, Bagherzadeh N. Method for designing ternary adder cells based on CNFETs. IET Circuits, Devices & Systems. 2017;11(5):465-470. DOI: 10.1049/iet-cds.2016.0443

- [4] Vudadha C, Surya A, Agrawal S, Srinivas MB. Synthesis of ternary logic circuits using 2:1 multiplexers. IEEE Trans. Circuits Syst. I. 2018;65(12):4313-4325. DOI: 10.1109/TCSI.2018".2838258

- [5] Shahrom E, Hosseini SA. A new low power multiplexer based ternary multiplier using CNTFETs. AEU - International Journal of Electronics and Communications. 2018;93:191-207. DOI:10.1016/j.aeue.2018.06.011

- [6] Sharma T, Kumre L. CNTFET-based design of ternary arithmetic modules. Circuits Syst Signal Process. 2019;38(10):4640-4666. DOI: 10.1007/s00034-019-01070-9

- [7] Kim S, Lee SY, Park S, Kim KR, Kang S. A logic synthesis methodology for low-power ternary logic circuits. in IEEE Transactions on Circuits and Systems I: Regular Papers. 2020;67(9):3138-3151. DOI: 10.1109/TCSI.2020.2990748

- [8] Mahmoudi Salehabad I, Navi K, Hosseinzadeh M. Two novel inverter-based ternary full adder cells using CNFETs for energy-efficient applications. International Journal of Electronics. 2020;107(1):82-98. DOI: 10.1080/00207217.2019.1636306

- [9] Hosseini SA, Etezadi S. A novel low-complexity and energy-efficient ternary full adder in nanoelectronics. Circuits Syst Signal Process. 2021;40(3):1314-1332. DOI: 10.1007/s00034-020-01519-2

- [10] Jaber RA, Haidar AM, Kassem A, Zahoor F. Ternary full adder designs employing unary operators and ternary multiplexers. Micromachines. 2023;14:1064. DOI: https://doi.org/10.3390/mi14051064

- [11] Etiemble D. Post algebras and ternary adders. Journal of Electrical Systems and Inf Technol. 2023;10:20. DOI: https://doi.org/10.1186/s43067-023-00088-z

- [12] Toulabinejad M, Taheri M, Navi K, Bagherzadeh N. Toward efficient implementation of basic balanced ternary arithmetic operations in CNFET technology. Microelectronics Journal. 2019;90:267-277. ISSN 0026-2692 DOI: https://doi.org/10.1016/j.mejo.2019.05.010

- [13] Kim S, Lim T, Kang S. An optimal gate design for the synthesis of ternary logic circuits. 2018 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), Jeju, Korea (South). 2018;476-481. DOI: 10.1109/ASPDAC.2018.8297369

- [14] Yoon J, Baek S, Kim S, Kang S. Optimizing ternary multiplier design with fast ternary adder. in IEEE Transactions on Circuits and Systems II: Express Briefs. 2023;70(2):766-770. DOI: 10.1109/TCSII.2022.3210282

- [15] Shahrom E, Hosseini SA. A new low power multiplexer based ternary multiplier using CNTFETs. AEU - International Journal of Electronics and Communications. 2018;93:191-207. DOI: https://doi.org/10.1016/j.aeue.2018.06.011

- [16] Tabrizchi S, Panahi A, Sharifi F, Mahmoodi H, Badawy AH. Energy-efficient ternary multipliers

- using cnt transistors. Electronics. 2020;9:643.

DOI: https://doi.org/10.3390/electronics9040643

- [17] Jaber RA, Haidar AM, Kassem A. CNTFET-based design of ternary multiplier using only multiplexers. 2020 32nd International Conference on Microelectronics (ICM), Aqaba, Jordan. 2020;1-4.

- DOI: 10.1109/ICM50269.2020.9331806

- [18] Jaber RA, Bazzi H, Haidar A, Owaidat B, Kassem A. 1-trit ternary multiplier and adder designs using ternary multiplexers and unary operators. 2021 International Conference on Innovation and Intelligence for Informatics, Computing, and

- Technologies (3ICT), Zallaq, Bahrain. 2021;292-297.

- DOI: 10.1109/3ICT53449.2021.9581366

- [19] Abbasian E, Sofimowloodi SA. A high-performance and energy-efficient ternary multiplier using CNTFETs. Arab J Sci Eng; 2023. DOI: https://doi.org/10.1007/s13369-023-07618-x

- [20] Etiemble D, Jaber RA. Design of (3,2) and (4,2) CNTFET ternary counters for multipliers. Asian Journal of Research in Computer Science. 2023;16(3):103-118.

- DOI:https://doi.org/10.9734/ajrcos/2023/v16i3349

- [21] Deng J, Wong HP. A compact spice model for carbon-nanotube field-effect transistors including nonidealities and its application-part II: Full device model and circuit performance benchmarking. in IEEE Transactions on Electron Devices. 2007;54(12):3195-3205.

- DOI: https://doi.org/10.1109/TED.2007.909043.

- [22] Townsend WJ, Swartzlander Jr. EE, Abraham JA. A comparison of Dadda and Wallace multiplier delays. Proc. SPIE 5205, Advanced Signal Processing Algorithms, Architectures, and Implementations XIII; 2003.

DOI: https://doi.org/10.1117/12.507012

© 2023 Etiemble and Jaber; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0) which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Peer-review history:

The peer review history for this paper can be accessed here:

https://www.sdiarticle5.com/review-history/110651